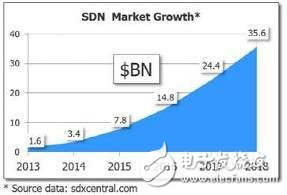

Eliminating complex network SoC development risks is no longer a distant goal; today, all design teams can do so. Recently, I have been writing a series of articles about using hardware accelerated simulation to verify the benefits of network system-on-a-chip (SoC) design before chip success. In this column, we'll look at a new way to bridge the gap between front-end and back-end verification in the same network design. Before we get into the details, let's take a look at this highly competitive market segment. As new markets such as cloud computing, big data centers, and mobile applications continue to emerge, software-driven networking (SDN) architectures are being adopted. Figure 1 shows the annual revenue of the SDN market trend, which is expected to increase by 135% in the next two years. Figure 1. Adoption of SDN continues to rise due to new markets such as cloud computing, big data centers and mobile applications (Source: Lauro RizzatTI) SDN has in turn significantly increased design complexity, scaled up the design, and increased the number of ports. Figure 2 plots the scale of design growth in some key market segments. Figure 2. Complexity and number of gates have increased with new SDN applications (Source: Lauro RizzatTI) The design team that developed these giant SoCs has long been overwhelmed, and the explosion of this overwhelming design scale poses many challenges. In descending order of importance, these challenges include: 1. Test all port configurations. 2. Measure and meet performance and bandwidth expectations. 3. Demonstration design supports all Ethernet OSI layer protocols of various specifications 4. Debug hardware problems found in hardware simulation and back-end issues in the lab. 5. Ensure that the design is reconfigured/executed by software as expected. 6. Provide fast turnaround time for compiling, downloading, and running. 7. Minimize the cost/time of deploying the verification environment. 8. Evaluate power consumption and minimize it. 9. Reduce the package of the chip. These challenges have not been solved by traditional software simulation tools or formal verification tools. This does not mean that these tools have become useless. On the contrary, they are the basic tools in the validation toolbox, but their deployment is limited to the scope of validation at the intellectual property (IP) module and subsystem module level, which is essential in the early development cycle of modern complex SoC design. Includes network chips. In the billion-level competition stage, only the hardware-driven verification engine can cope with these challenges, and it is in line with a compact schedule to avoid potential revenue loss caused by chip release delays in the fast-growing network market. The author's previous article has been mentioned many times. In the hardware-based verification engine, hardware accelerated simulation has become the best tool for front-end verification. Modern hardware accelerators have near-infinite capacity to simulate the largest designs and provide overall design visibility and access/control without instrumentation/compilation, while also supporting high throughput and fast, predictable compilation and recall times. It can accommodate multiple concurrent users by optimizing the use of resources. It can be deployed in multiple modes of operation to perform a variety of verification tasks, including internal circuit simulation (ICE) and virtual testing, low power verification, power estimation, performance feature extraction, and testability design (DFT). When using multiple ports to verify network SoC designs -- such as 64 or more -- ICE value positioning has been significantly lower than in the previous decade. The ICE environment requires external hardware such as a speed adapter as an interface for fast real-world network traffic (hundreds of megahertz) and relatively low-speed hardware-accelerated emulation (one megahertz or several megahertz). The setup complexity is increased, power consumption is increased, and reliability is reduced. As a result, the reconfiguration of the settings becomes cumbersome and slow to deploy, limiting the use of the accelerator to a single user installed locally, thus eliminating remote access. Worse, it makes the reproducibility and repeatability of design debugging uncertain, making debugging plans difficult to implement. Instead, the design team is migrating from the ICE setup to the virtual test environment, eliminating any hardware--and-all hardware dependencies, including noise, power, cabling, reliability, and related costs. Virtual hardware can be created by using a combination of software and synthesizable hardware models to make it easy to reconfigure with the software before the actual hardware is available. They run at hardware accelerated simulation speeds, support multiple users and multiple projects, are remotely accessible, and can be deployed in the data center. Guy Hutchison of the DAC 2016 expert group (Cavium's assistant vice president and also a hardware engineer) said: "For our design, we only use virtual technology. Partly because of the nature of our design -- for us, there is no A truly representative target that can reach 100 gigabytes of traffic. The internal circuit simulator approach is of no value to us, so we use a completely virtual approach to all simulations." However, virtual mode requires the creation of a virtual test environment, which is an extraordinary task. In this regard, Mentor Graphics has taken the lead in developing a comprehensive complex virtual environment, VirtuaLAB, to support front-end testing of application-specific SoC designs. In the case of network design, VirtuaLAB includes an Ethernet Packet Generator and Monitor (EPGM) that generates, transmits, and monitors Ethernet packets for the design under test (DUT). It can be configured with 25GMII, 50GMII, 200GMII and 400GMII.

When you think of the screen protectors of old, you're probably thinking of TPU. It's a flexible plastic that's a huge hassle to install . it's flexible, so it can go edge-to-edge on any phone, it has better impact protection than PET, and it has limited "self-healing" powers for small scratches. Brands like TUOLI offer TPU at very affordable prices,

On the other hand, TUOLI's comes in a few different styles depending on the look, feel, and features you want.

Tpu Screen Protector,Hydrogel Protective Film,Mobile Phone Screen Protector,Tpu Hydrogel Film,hydrogel protector, hydrogel sheet Shenzhen TUOLI Electronic Technology Co., Ltd. , https://www.szhydrogelprotector.com