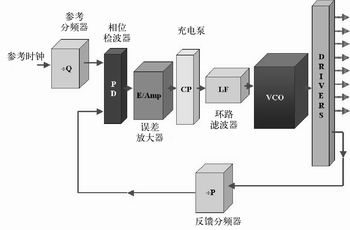

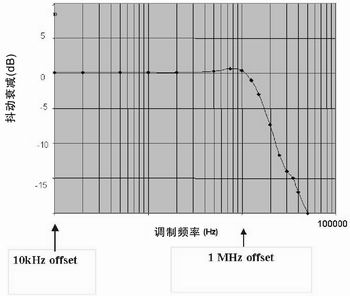

Along with the rapid development of the communication market, the complex tree structure for clock distribution has been widely used. A clock tree is required in order to feed a number of nodes that are clocked and otherwise designed to transmit data (designing combination units through numerous different functions with digital time domain accuracy). Since a large number of clocks are required to time multiple nodes in the system, it is imperative to generate these timing clocks in a strict and very accurate and limited window time. Figure 1 Phase-Locked Loop (PLL) Figure 2 Typical jitter transfer function curve for a zero delay buffer

Currently, these windows are measured in picoseconds. As the number of nodes that must feed signals and the rapid reduction of the timing window into which the clock must be placed, designers must understand the characteristics of the devices used to complete the generation, multiplication, and transmission of these clock signals. Many of today's clock signal generation and transmission products include PLLs, which further increases the complexity of timing systems. These PLLs enable designers to retime the hysteresis or advanced clocks, eliminate the propagation delays that occur during long-distance clock signal transmission, and generate clock signals that are phase-locked to a reference clock and have different frequencies.

While using the PLL to obtain these clock control capabilities, it also brings about degradation of PLL reliability. It is necessary to understand and provide some tolerance for the deterioration of the signal quality produced by all PLL-based clock processing components. The noise added by the PLL to the clock signal it processes cannot be completely eliminated. This noise is often tolerated, and the components of the PLL that are located in the clock tree can be configured to control them. The resulting noise is controlled and the total clock tree performance is much higher than the acceptable minimum.

The accumulation of noise applied by the PLL to the clock signal passed or generated by it is jitter. In electrical terms, jitter refers to the time offset of a specified clock point (usually a rising or falling edge of a pulse at a specified voltage) relative to its absolute desired point. This type of jitter has traditionally been divided into two broad categories. The first type is short-term jitter, which is measured based on the displacement of the time point relative to its ideal position in an adjacent clock cycle. A common term used for this parameter is cycle-to-cycle jitter.

Another type of jitter is measured over a longer period of time. One term used for such jitter is long-term jitter. The term used with higher frequency and accuracy is long-term period jitter. In this field, a length of time (in cycles or seconds) must be specified to limit the sampling period of the event to produce a measured value. If there is no limit to the sampling period, the event may drift at an indeterminate position. Therefore, the measurement period for measuring the incidence of the event must be set and described in order to more precisely specify the specific method of measurement. For a particular application, it is usually related to the stability that the pulse edge must have within a certain period of time.

In the process of establishing a clock tree with a reasonable value, it is inevitable to connect the PLL-based clock processing elements in series. In this case, it is necessary to understand the interaction between the jitters caused by each component, and more importantly, to understand the jitter content of all the final component clocks generated by the clock tree. This article will be comprehensively discussed from the perspective of principles and functions.

When engineers are ready to adopt a design that includes multiple serial PLL clock processing components, they often face two sources of information. The first source of information is the traditional knowledge owned by RF designers. Although there are many introductions to RF-based PLL designs, they often involve circuits that combine two PLL-based signals to generate one and several clocks or differential clocks. Moreover, they generally do not have picosecond timing limitations like digital designs. There is a lot of theoretical information available in the field of digital clocks, but what the designer needs is some empirical information or evidence to turn the application puzzle into a clear and predictable view that clearly defines the design goals and should Focus on design time and resources to achieve a robust design.

This article will examine the performance of a special and typical experiment using five series PLLs. Although we do not recommend the design of a series configuration of five PLL devices, this program is specifically used to reflect the adverse effects of the designer's concerns.

One of the first things to understand when studying PLL-based clock processing components is their role in the clock signals that must pass through them. Figure 1 shows a typical ZDB (Zero Delay Buffer) component and its components.

The most important for electrical performance is the series element group consisting of a phase detector, an error amplifier, a charge pump, and a loop filter. For an input reference clock signal, these components function as a second-order low-pass filter. Figure 2 shows the jitter and frequency transfer functions and the bandwidth response of the device used in this example.

This is an input-output transfer function graph. It indicates the gain (and loss) to any input frequency of the component. Note that the input frequency (either the frequency itself or the input reference signal) will be transmitted and amplified by the loop filter and phase detector combination stage. Frequencies above the 1.5MHz roll-off point (and the frequency components of the complex wave) will be attenuated by this filtering and will be suppressed as it passes through the device.

In order to analyze and explain the effect of the PLL clock processing device on the clock signal transmitted through it, three different views will be examined in the following for the noise present on the clock signal through several successive stages.

The first is the frequency domain view. This view will use a spectrum analyzer to observe a plot of power level versus frequency to see how this noise propagates through the system.

The second is a long-period jitter view. Here you can see how the output clock works over a long period of time, as well as the actual frequency distribution of these periodic changes. This measurement will show the correlation between the amount of occurrence (total) and the frequency by means of a TIA (Time Interval Analyzer).

The third is the modulation domain view. A frequency-to-period (CC) or frequency change between adjacent cycles in a series of medium length periods can be observed in this view. It will show the presence of a pulse or real-time frequency (jitter) and a view of a medium time period.

The devices used in this article have the following data sheet characteristics:

• 200 ps CC jitter • 1 MHz PLL loop bandwidth There is a fairly flat noise floor on either side of the reference carrier frequency. The width and slope of the carrier sweep depends on the spectrum analyzer's video performance and resolution bandwidth settings. It is important to note the flatness of the rising and falling edges of the noise floor relative to the reference clock pulse, since we are concerned with the variation of this flatness between processing stages.

As can be seen from FIG. 2 and the related description, the PLL-based clock device functions as a low-pass second-order filter in the frequency domain. In the process of studying the spectral content of each successive stage, it is clear that the noise located within the passband of the loop filter is passed through successive stages and amplified step by step. In fact, for the output of the second and subsequent stages, the spectral energy delivered by these has a certain peaking. It corresponds to a slight peaking at the edge of the pass band shown in FIG. The second thing to be concerned with is the noise layer outside the passband of the device. Note that even after the 5-level gain, the noise floor is still close to the input signal (topmost and bottommost) levels of the waveform amplitude.

For frequencies close to the reference frequency, the PLL-based clock device does function as a low-pass filter. Low frequency (near carrier frequency) energy and signal components will easily pass through the device. This means that the low frequency energy (which, in performance, will be converted to a low frequency and slow moving or drifting of the output frequency) will be transmitted and amplified as the signal passes through successive processing stages. Who will control its final value (the deviation from the input reference to the first stage in frequency) depends almost entirely on the bandwidth of the device and any other effort to suppress it between stages of the clock tree.

The second view we will study is a long-term or periodic jitter view.

The first thing to note is that the density distribution is essentially a Gaussian function. This provides support for the known fact that random jitter caused by actual noise inside the component or inherent white noise in the input signal will appear as a highly predictable Gaussian spread (frequency modulation) on the signal. effect. The second thing to note is the effect of this noise on the total amplitude of the clock signal at multiple processing stages, as well as the accumulation and broadening of the noise as it passes through each additional processing stage (distributed over a wider range of frequencies).

It should be noted that these frequencies are close to the fundamental frequency. This is in line with this point of view because it indicates that the noise and energy components near the device passband (or within the device passband) are not only transmitted by the device that amplifies it. Also, since the noise (jitter) is close to the operating frequency of the device, the rate of occurrence of jitter is very slow. It is based on the fact that the overall effect is to make the second stage track the error of the first stage signal, the third stage to track the error of the first stage and the second stage, and the last stage to track the accumulation of all the processing stages in front of it ( Additive) error.

The high frequency domain period to the period jitter of the clock is accumulated between the stages, and its increment is very small. In some systems, it will even decrease as it passes through certain processing stages. The reason for this is that cycle-to-cycle jitter occurs between adjacent cycles of the clock. In this example, the clock's fundamental frequency is 106.25 MHz. In order for the waveform to respond to an impulse noise (short-term and high-frequency portions of the spectral frequency content), its frequency will have to be above 100 MHz. Otherwise, the effects of noise are spread over many cycles. Due to the narrow loop bandwidth of the device, this energy is filtered out through the edges of the bandpass curve and is therefore not easily propagated between stages. In a precisely designed system, a wide bandwidth element can be used to pass such artificial modulation interference as a desired EMI suppression spread spectrum modulated signal (at a cycle rate of less than 35 kHz). Therefore, in order to reduce the accumulated high frequency jitter of the system, a very narrow bandwidth PLL device can be used to effectively filter out this and other high frequency noise before applying the target system device.

Summarize what is stated in this example. First, when the signal passes through a continuous PLL-based clock processing stage, the low frequency noise contained within the bandpass characteristics of the PLL-based device will propagate and be amplified and accumulated. If the system being designed is a time base (clock) that requires long-term stability and is not adversely affected by the instantaneous turn-off frequency, then the method of connecting the PLL clock processing devices in series has minimal impact on the system. Due to the long-term Gaussian balance process, any short-cycle changes will eventually be balanced.

Therefore, if two to three consecutive clocks are used to very closely align the events in the system, this is not a problem because the accumulation time of the long-cycle jitter is too long, so it is impossible to form enough for adjacent clock cycles. The event that occurred has an impact error. In these applications, it is common practice to time the dynamic memory, the CPU, and other devices that pass data to them. Here, the stability of three consecutive clocks in a RAS-CAS-READ cycle has a crucial impact in an instant, but long-period changes over a 1000-cycle span have little effect.

On the other side of the spectrum, jitter that is very fast (far beyond the PLL bandwidth used by the device) is not passed through systems with multiple PLL-based clocking devices. The period-to-cycle jitter present at the output of any device is itself much different from the jitter to the device under test. This means that devices that are very sensitive to cycle/frequency variations in adjacent or very close cycles of their clock pulses are expected to work well with serial, PLL-based clock device trees. The main negative impact on applications employing PLL-based serial clock device trees arises in specific data applications where one input data stream has many consecutive data bits that are split into very specific and scattered time windows. In such applications, long-term displacement of the clock generated by a long PLL-based component tree may result in the clock signal falling outside of the desired unit time domain when restoring data from the data stream.